PLL用法

易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对应的。对于易灵思的FPGA来讲,PLL,GPIO,MIPI,LVDS和DDR相对于core部分都是外设。而这些外设的设置都是在interface designer中的。下面以pll的添加为例,对于trion系列的设置简单说明。钛金系列会稍微的区别,但是只要了解了一个,另一个都是大同小异的。

一、PLL的添加

(1)打开interface desinger。

(2)选择pll 右击选择Create block,就可以添加pll

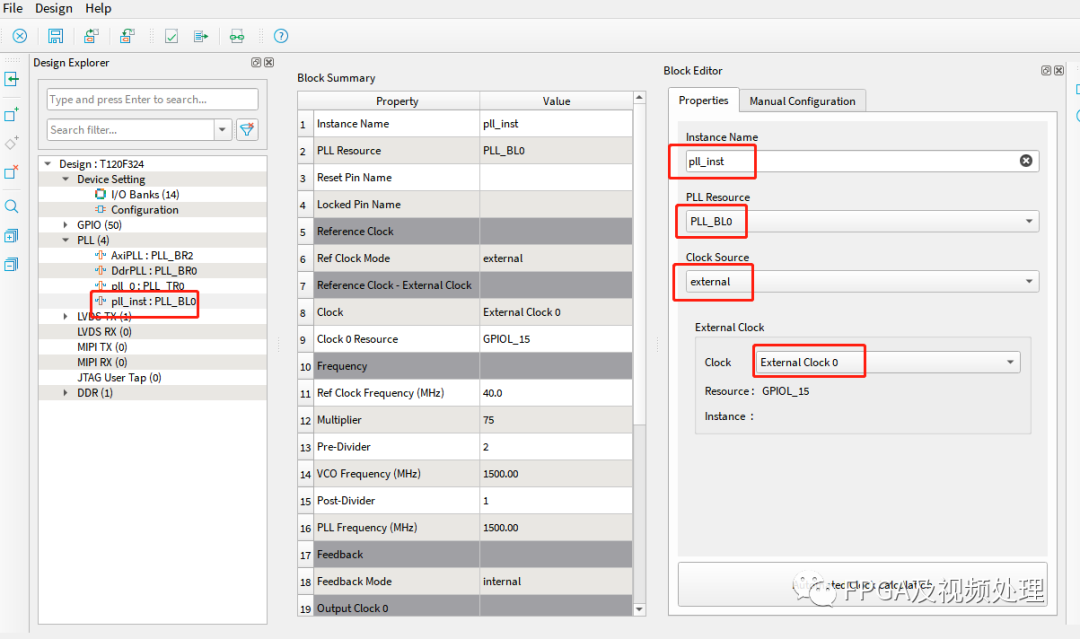

(3)这里我们把pll的例化名修改为pll_inst,并且按回车(必须回车)。

PLL resource对应PLL的位置,这也是易灵思的PLL使用与别家有区别的地方,必须要指定PLL的位置。

clock source是指pll参考时钟的源来自哪里,包括外部和内部。

External clock:指示参考时钟的源,包括参考时钟0,参考时钟1。

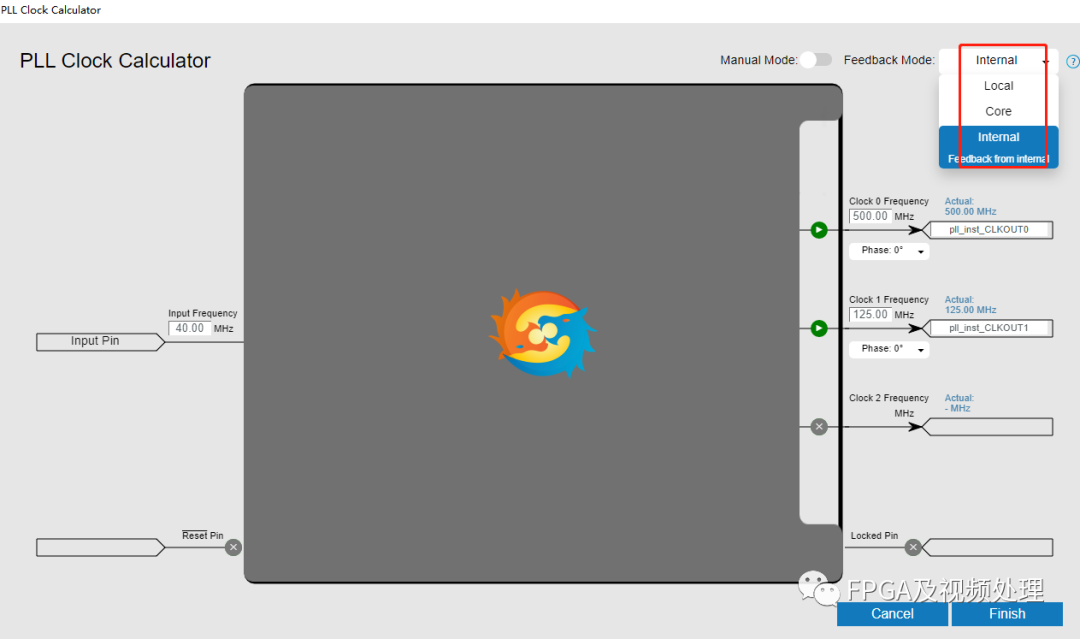

(4)点击Automated Clock Calculation打开时钟设置界面。trion最多可以设置3个时钟,红包框中的箭头和x可以用于打开和关闭相应的时钟。

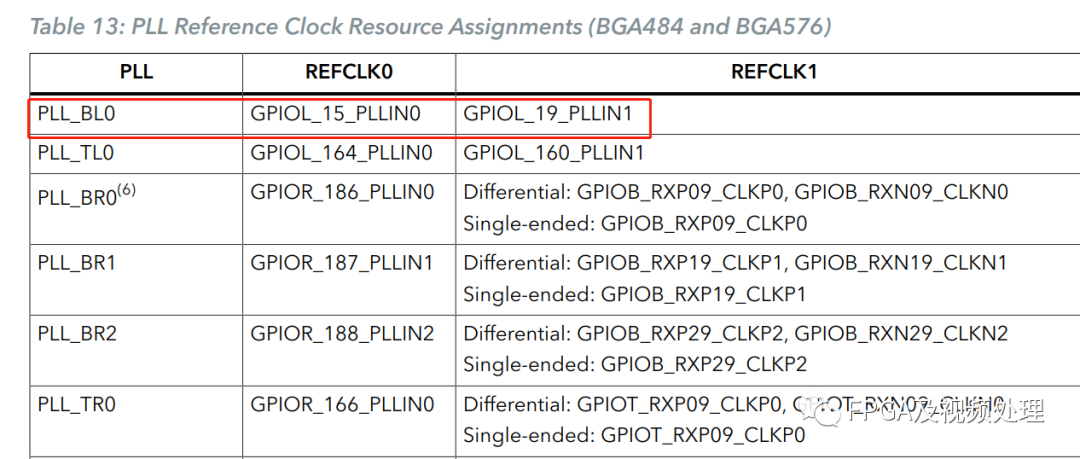

(5)设置完成上面的操作之后,我们需要指定PLL的参考时钟来源。从ds上我们可以看到PLL_BL0有两个时钟源,分别是REFCLK0和REFCLK1,分别对应GPIOL_15_PLLIN0和GPIOL_19_PLLIN1。

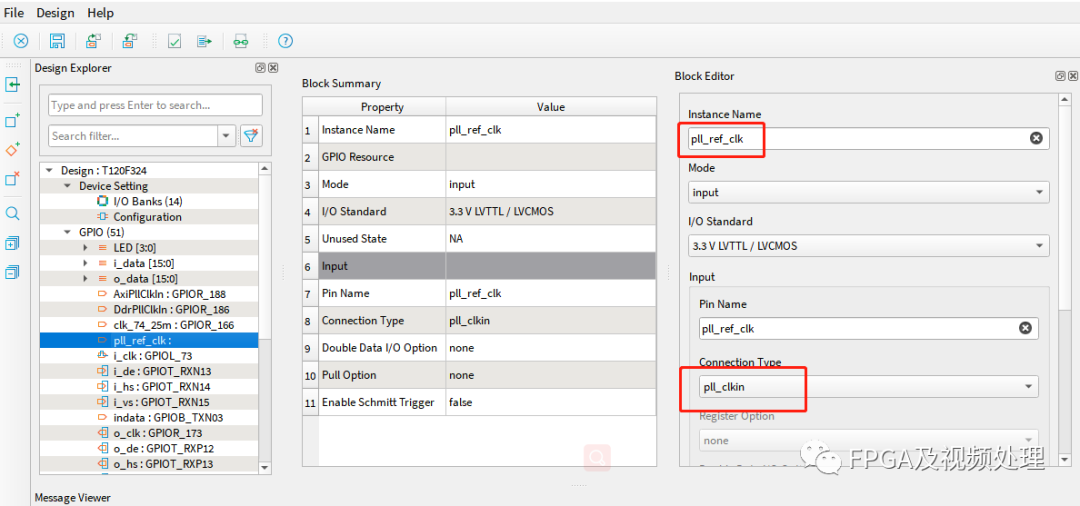

然后再添加PLL的参考时钟脚,这里我们例化为pll_ref_clk,并要把connection Type设置为pll_clkin。并分配到GPIOL_15_PLLIN0上,因为上面选择了External Clock0。这样PLL的设置就差不多了。

二、关于时钟源

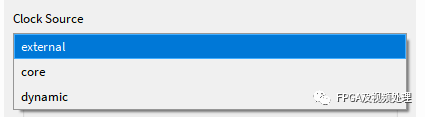

在选择clock source时,有三个选项,分别是external, core和dynamic。

external好理解,就是参考时钟从外部IO进入的,上面的设置就是。

core是指时钟从FPGA内部给PLL的参考,比如一个PLL的输出给另一个PLL做参考时,第二个PLL的参考就是设置成core,或者从GCLK进入FPGA再环到PLL的输入。

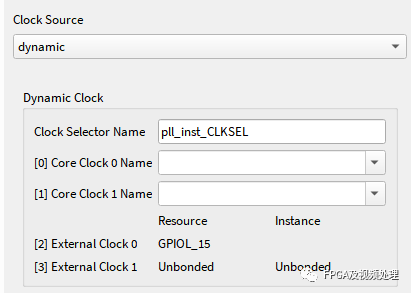

至于Dynamic Clock就是动态输入选择,支持多路选择,如下图,可以支持两个core和两个external时钟。但是因为PLL不支持动态重配置,所以这个功能应用有限。

三、PLL的反馈方式

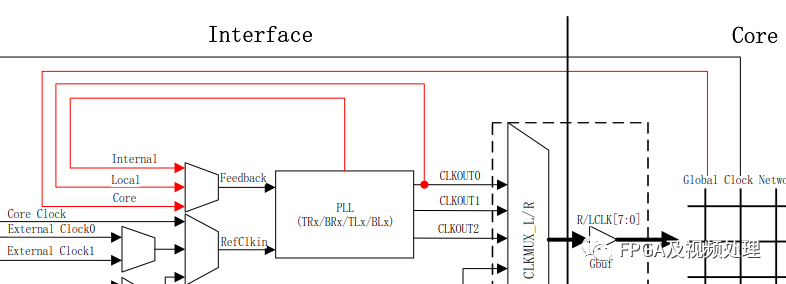

PLL有三种反馈,core,Local和internal。

从下面的图来看,不同的反馈位置是不一样的。core的反馈路径是从FPGA的core内部来反馈,可以保证输入时钟与输出时钟同频同相。这在源同步设计中是很有用的。而local和internal可以支持输出更多的频率,大家可以在操作中发现如果是core反馈的话,有些频率是设置不出来的,而local和interanl却可以。

关于PLL的注意事项

(1) PLL的反馈时钟的频率不能超过refclk的4倍。

(2)经常会有客户反应上电之后PLL存在失锁的情况,这是什么原因呢?这个是因为上电时PLL的参考时钟不稳定,造成PLL不能锁定在固定的频率,这样之后,即使后继参考时钟稳定也不能锁定。

那解决方案是什么呢?要求等参考时钟稳定之后再释放PLL的复位,或者等参考时钟稳定之后再复位一次。

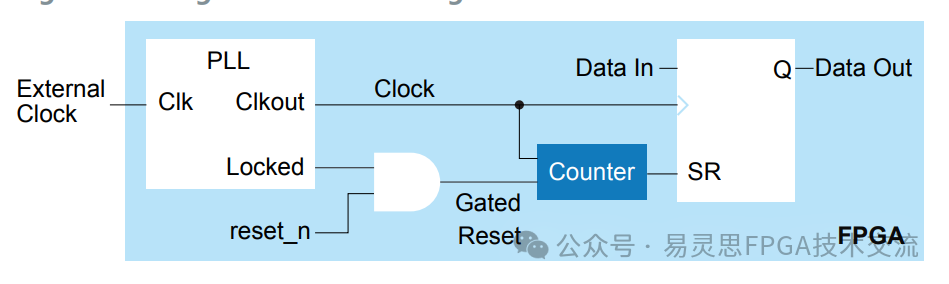

(3)当需要使用PLL的locked信号做为复位时,要求pll的locked信号拉高25us之后再释放复位。如下图,在locked信号之后添加计数器,记数到25us之后释放器件的SR。

上面描述其实描述相对粗糙,语句什么的也没有太去考虑措辞,花半个小时BB下,能用起来就行,如果实在有看不懂的,欢迎留言。

审核编辑 黄宇

- 随机文章

- 热门文章

- 单波224Gbps误码分析仪—满足1.6T算力接口误码测试需求

- PLL用法

- 信号发生器AFG31052在多载波信号生成中的应用

- 猿声科技完成新一轮战略融资,柯力传感出手 看好多维触觉技术

- 如何实现CX变频器与PLC间的通信?

- 被收购后,浙江温度传感器龙头终止挂牌“新三板”

- 中国科学院上海微系统所开发出高性能10mm大口径压电 MEMS 快反镜

- 开疆智能ModbusTCP转Canopen网关连接汇川AM403PLC与编码器配置案例

- “京剧文化之旅”亮相莫斯科 深化中俄文旅交流

- 戏剧舞台也要“节能减排”

- 1感染甲流后该如何科学调养?饮食起居这样做,感染甲流后该如何科学调养?饮食起居这样做

- 2马克龙去的这所大学,太宝藏了吧!,马克龙去的这所大学,太宝藏了吧!

- 3北方多地迎来降雪降温天气 各部门联动“战”寒潮筑牢安全防线,北方多地迎来降雪降温天气 各部门联动“战”寒潮筑牢安全防线

- 4“无保护”攀岩真的无保护吗?“无保护”攀岩真的无保护吗?

- 5福州发布公告:吴石故居将封闭施工,展开系统性修缮

- 6科学家的照片排在董事长之上,科学家的照片排在董事长之上

- 711月份“菜篮子”产品价格呈现季节性上涨 多因素推高生产成本,11月份“菜篮子”产品价格呈现季节性上涨 多因素推高生产成本

- 8城中话债|激活民间投资:让有效率的资本站上C位

- 9何立峰:有力有序有效做好2026年金融重点工作

- 10晚间重磅!又一万亿级券商将诞生 券业并购潮涌